# 1.5-A, 60-V, STEP-DOWN SWIFT™ DC/DC CONVERTER WITH ECO-MODE™

Check for Samples: TPS54160

### **FEATURES**

- 3.5-V to 60-V Input Voltage Range

- 200-mΩ High-Side MOSFET

- High Efficiency at Light Loads with a Pulse Skipping Eco-Mode™

- 116-μA Operating Quiescent Current

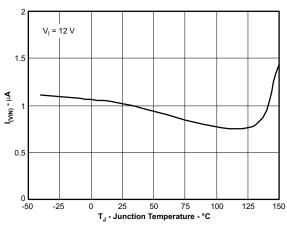

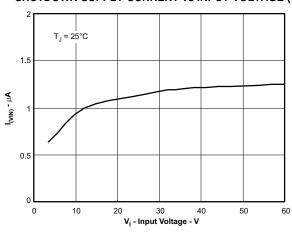

- 1.3-μA Shutdown Current

- 100-kHz to 2.5-MHz Switching Frequency

- Synchronizes to External Clock

- Adjustable Slow Start/Sequencing

- UV and OV Power Good Output

- Adjustable UVLO Voltage and Hysteresis

- 0.8-V Internal Voltage Reference

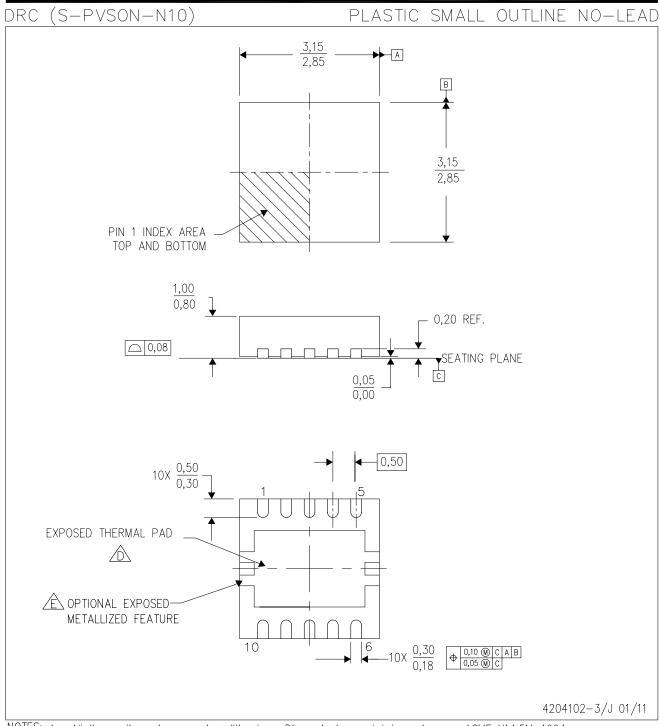

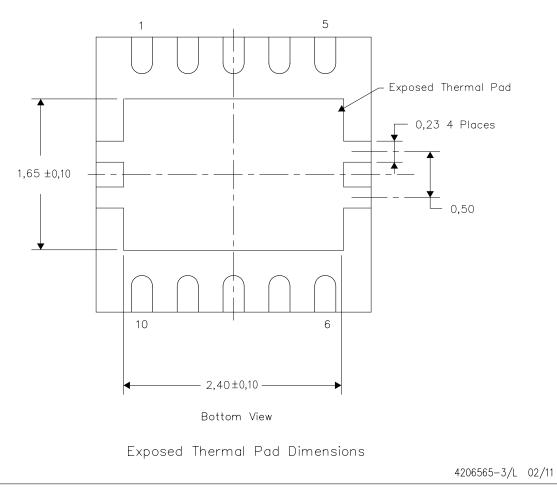

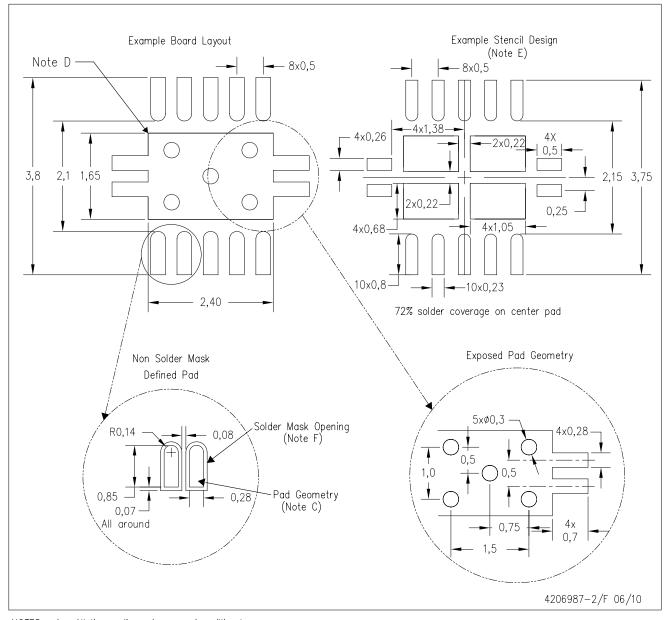

- MSOP-10 Package With PowerPAD™

- Supported by SwitcherPro<sup>™</sup> Software Tool (http://focus.ti.com/docs/toolsw/folders/print/s witcherpro.html)

- For SWIFT™ Documentation, See the TI Website at http://www.ti.com/swift

#### **APPLICATIONS**

- 12-V, 24-V and 48-V Industrial and Commercial Low Power Systems

- Aftermarket Auto Accessories: Video, GPS, Entertainment

#### DESCRIPTION

The TPS54160 device is a 60-V, 1.5-A, step down regulator with an integrated high-side MOSFET. Current mode control provides simple external compensation and flexible component selection. A low ripple pulse skip mode reduces the no load, regulated output supply current to 116  $\mu$ A. Using the enable pin, shutdown supply current is reduced to 1.3  $\mu$ A.

Under voltage lockout is internally set at 2.5 V, but can be increased using the enable pin. The output voltage startup ramp is controlled by the slow start pin that can also be configured for sequencing/tracking. An open drain power good signal indicates the output is within 93% to 107% of its nominal voltage.

A wide switching frequency range allows efficiency and external component size to be optimized. Frequency fold back and thermal shutdown protects the part during an overload condition.

The TPS54160 is available in 10-pin thermally enhanced MSOP PowerPAD package.

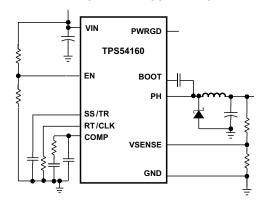

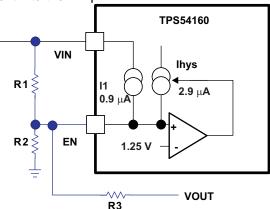

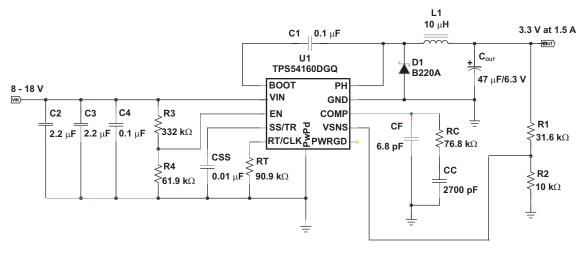

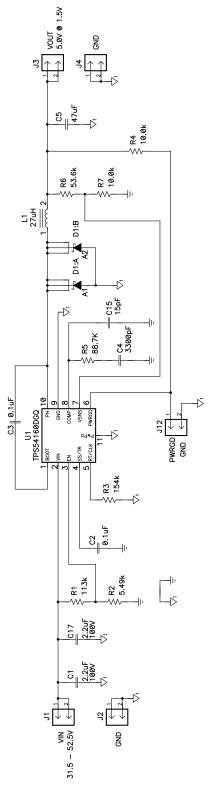

### SIMPLIFIED SCHEMATIC

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

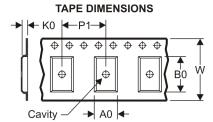

### Table 1. ORDERING INFORMATION<sup>(1)</sup>

| T <sub>J</sub> | PACKAGE     | TRANSPORT MEDIA | QUANTITY | PART NUMBER  |

|----------------|-------------|-----------------|----------|--------------|

| -40°C to 150°C | 10-Pin MSOP | Tube            | 80       | TPS54160DGQ  |

|                |             | Tape and Reel   | 2500     | TPS54160DGQR |

<sup>(1)</sup> For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

#### ABSOLUTE MAXIMUM RATINGS(1)

Over operating temperature range (unless otherwise noted)

|                                                          |                     | VALUE         | UNIT  |  |

|----------------------------------------------------------|---------------------|---------------|-------|--|

|                                                          | VIN                 | -0.3 to 65    |       |  |

|                                                          | EN <sup>(2)</sup>   | -0.3 to 5     |       |  |

|                                                          | BOOT                | 73            |       |  |

| Lament and the ma                                        | VSENSE              | -0.3 to 3     | V     |  |

| Input voltage                                            | COMP                | -0.3 to 3     | \ \ \ |  |

|                                                          | PWRGD               | -0.3 to 6     |       |  |

|                                                          | SS/TR               | -0.3 to 3     |       |  |

|                                                          | RT/CLK              | -0.3 to 3.6   |       |  |

|                                                          | воот-рн             | 8             |       |  |

| Output voltage                                           | PH                  | -0.6 to 65    | V     |  |

|                                                          | PH, 10-ns Transient | -2 to 65      |       |  |

| Voltage Difference                                       | PAD to GND          | ±200          | mV    |  |

|                                                          | EN                  | 100           | μА    |  |

|                                                          | BOOT                | 100           | mA    |  |

| Source current                                           | VSENSE              | 10            | μА    |  |

|                                                          | PH                  | Current Limit | Α     |  |

|                                                          | RT/CLK              | 100           | μА    |  |

|                                                          | VIN                 | Current Limit | А     |  |

| 0:-1                                                     | COMP                | 100           | μА    |  |

| Sink current                                             | PWRGD               | 10            | mA    |  |

|                                                          | SS/TR               | 200           | μА    |  |

| Electrostatic Discharge (HBM) QSS 009-105 (JESD22-A114A) |                     | 1             | kV    |  |

| Electrostatic Discharg                                   | 500                 | V             |       |  |

| Operating junction ten                                   | -40 to 150          | °C            |       |  |

| Storage temperature                                      | Storage temperature |               |       |  |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) See the Enable section and Adjusting Undervoltage Lockout section of this datasheet for details.

Submit Documentation Feedback

Copyright © 2008–2010, Texas Instruments Incorporated

#### THERMAL INFORMATION

|                   |                                                                      | TPS54160 |       |

|-------------------|----------------------------------------------------------------------|----------|-------|

|                   | THERMAL METRIC <sup>(1)(2)</sup>                                     | DGQ      | UNITS |

|                   |                                                                      | 10 PINS  |       |

| $\theta_{JA}$     | Junction-to-ambient thermal resistance (standard board)              | 62.5     |       |

| $\theta_{JA}$     | Junction-to-ambient thermal resistance (custom board) <sup>(3)</sup> | 57       |       |

| $\theta_{JCtop}$  | Junction-to-case (top) thermal resistance                            | 83       |       |

| $\theta_{\sf JB}$ | Junction-to-board thermal resistance                                 | 28       | °C/W  |

| ΨЈТ               | Junction-to-top characterization parameter                           | 1.7      |       |

| ΨЈВ               | Junction-to-board characterization parameter                         | 20.1     |       |

| $\theta_{JCbot}$  | Junction-to-case (bottom) thermal resistance                         | 21       |       |

- (1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

- Power rating at a specific ambient temperature TA should be determined with a junction temperature of 150°C. This is the point where distortion starts to substantially increase. See power dissipation estimate in application section of this data sheet for more information

- (3) Test boards conditions:

- (a) 3 inches x 3 inches, 2 layers, thickness: 0.062 inch

- (b) 2 oz. copper traces located on the top of the PCB

- (c) 2 oz. copper ground plane, bottom layer (d) 6 thermal vias (13mil) located under the device package

## **ELECTRICAL CHARACTERISTICS**

$T_1 = -40$ °C to 150°C. VIN = 3.5 to 60V (unless otherwise noted)

| PARAMETER                                                  | TEST CONDITIONS                                                          | MIN   | TYP    | MAX   | UNIT  |  |

|------------------------------------------------------------|--------------------------------------------------------------------------|-------|--------|-------|-------|--|

| SUPPLY VOLTAGE (VIN PIN)                                   |                                                                          |       |        |       |       |  |

| Operating input voltage                                    |                                                                          | 3.5   |        | 60    | V     |  |

| Internal undervoltage lockout threshold                    | No voltage hysteresis, rising and falling                                |       | 2.5    |       | V     |  |

| Shutdown supply current                                    | EN = 0 V, 25°C, 3.5 V ≤ VIN ≤ 60 V                                       |       | 1.3    | 4     |       |  |

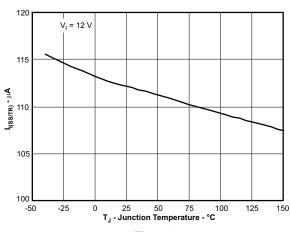

| Operating : nonswitching supply current                    | VSENSE = 0.83 V, VIN = 12 V, 25°C                                        |       | 116    | 136   | μА    |  |

| ENABLE AND UVLO (EN PIN)                                   |                                                                          | •     |        |       |       |  |

| Enable threshold voltage                                   | No voltage hysteresis, rising and falling, 25°C                          | 0.9   | 1.25   | 1.55  | V     |  |

| longs ourrons                                              | Enable threshold +50 mV                                                  |       | -3.8   |       | μА    |  |

| Input current                                              | Enable threshold –50 mV                                                  |       | -0.9   |       |       |  |

| Hysteresis current                                         |                                                                          |       | -2.9   |       | μΑ    |  |

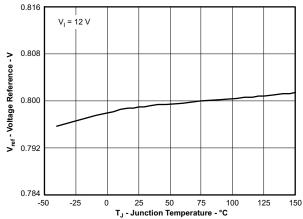

| VOLTAGE REFERENCE                                          |                                                                          |       |        |       |       |  |

| Voltage reference                                          | $T_J = 25^{\circ}C$                                                      | 0.792 | 0.8    | 0.808 | V     |  |

| voltage reference                                          |                                                                          | 0.784 | 0.8    | 0.816 | V     |  |

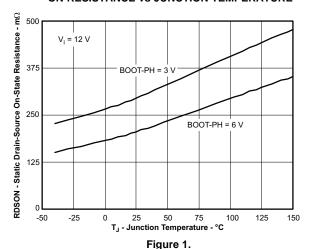

| HIGH-SIDE MOSFET                                           |                                                                          |       |        |       |       |  |

| On-resistance                                              | VIN = 3.5 V, BOOT-PH = 3 V                                               |       | 300    |       | mΩ    |  |

| Off-resistance                                             | VIN = 12 V, BOOT-PH = 6 V                                                |       | 200    | 410   | 11122 |  |

| ERROR AMPLIFIER                                            |                                                                          |       |        |       |       |  |

| Input current                                              |                                                                          |       | 50     |       | nA    |  |

| Error amplifier transconductance $(g_M)$                   | $-2 \mu A < I_{COMP} < 2 \mu A, V_{COMP} = 1 V$                          |       | 97     |       | μMhos |  |

| Error amplifier transconductance $(g_M)$ during slow start | $-2 \mu A < I_{COMP} < 2 \mu A, V_{COMP} = 1 V,$<br>$V_{VSENSE} = 0.4 V$ |       | 26     |       | μMhos |  |

| Error amplifier dc gain                                    | V <sub>VSENSE</sub> = 0.8 V                                              |       | 10,000 |       | V/V   |  |

| Error amplifier bandwidth                                  |                                                                          |       | 2700   |       | kHz   |  |

| Error amplifier source/sink                                | V <sub>(COMP)</sub> = 1 V, 100-mV overdrive                              |       | ±7     |       | μА    |  |

| COMP to switch current transconductance                    |                                                                          |       | 6      |       | A/V   |  |

Product Folder Link(s): TPS54160

## **ELECTRICAL CHARACTERISTICS (continued)**

$T_J = -40$ °C to 150°C, VIN = 3.5 to 60V (unless otherwise noted)

| PARAMETER           |                                             | TEST CONDITIONS                                | MIN | TYP  | MAX  | UNI |

|---------------------|---------------------------------------------|------------------------------------------------|-----|------|------|-----|

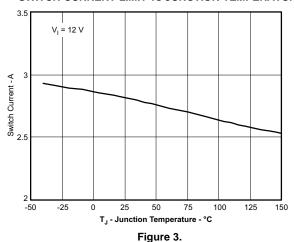

| CURRENT             | T LIMIT                                     |                                                |     |      |      |     |

|                     | Current limit threshold                     | VIN = 12 V, T <sub>J</sub> = 25°C              | 1.8 | 2.7  |      | Α   |

| THERMAL             | L SHUTDOWN                                  | 1                                              |     |      |      |     |

|                     | Thermal shutdown                            |                                                |     | 182  |      | °C  |

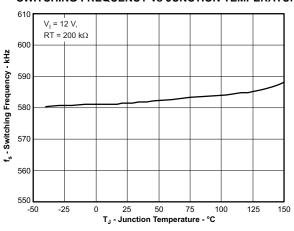

| TIMING R            | ESISTOR AND EXTERNAL CLOCK (R               | T/CLK PIN)                                     |     |      |      |     |

|                     | Switching frequency range using RT mode     |                                                | 100 |      | 2500 | kHz |

| sw                  | Switching frequency                         | $R_T = 200 \text{ k}\Omega$                    | 450 | 581  | 720  | kHz |

|                     | Switching frequency range using CLK mode    |                                                | 300 |      | 2200 | kHz |

|                     | Minimum CLK input pulse width               |                                                |     | 40   |      | ns  |

|                     | RT/CLK high threshold                       |                                                |     | 1.9  | 2.2  | V   |

|                     | RT/CLK low threshold                        |                                                | 0.5 | 0.7  |      | V   |

|                     | RT/CLK falling edge to PH rising edge delay | Measured at 500 kHz with RT resistor in series |     | 60   |      | ns  |

|                     | PLL lock in time                            | Measured at 500 kHz                            |     | 100  |      | μS  |

| SLOW ST             | ART AND TRACKING (SS/TR)                    |                                                |     |      |      |     |

|                     | Charge current                              | V <sub>SS/TR</sub> = 0.4 V                     |     | 2    |      | μΑ  |

|                     | SS/TR-to-VSENSE matching                    | V <sub>SS/TR</sub> = 0.4 V                     |     | 45   |      | mV  |

|                     | SS/TR-to-reference crossover                | 98% nominal                                    |     | 1.0  |      | V   |

|                     | SS/TR discharge current (overload)          | VSENSE = 0 V, V(SS/TR) = 0.4 V                 |     | 112  |      | μΑ  |

|                     | SS/TR discharge voltage                     | VSENSE = 0 V                                   |     | 54   |      | mV  |

| POWER G             | GOOD (PWRGD PIN)                            |                                                |     |      |      |     |

|                     |                                             | VSENSE falling                                 |     | 92%  |      |     |

| .,                  | VOENCE threehold                            | VSENSE rising                                  |     | 94%  |      |     |

| V <sub>VSENSE</sub> | VSENSE threshold                            | VSENSE rising                                  |     | 109% |      |     |

|                     |                                             | VSENSE falling                                 |     | 107% |      |     |

|                     | Hysteresis                                  | VSENSE falling                                 |     | 2%   |      |     |

|                     | Output high leakage                         | VSENSE = VREF, V(PWRGD) = 5.5 V, 25°C          |     | 10   |      | nA  |

|                     | On resistance                               | I(PWRGD) = 3 mA, VSENSE < 0.79 V               |     | 50   |      | Ω   |

|                     | Minimum VIN for defined output              | V(PWRGD) < 0.5 V, II(PWRGD) = 100 μA           |     | 0.95 | 1.5  | V   |

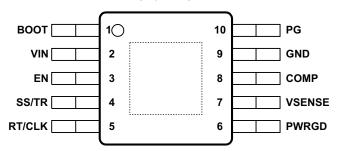

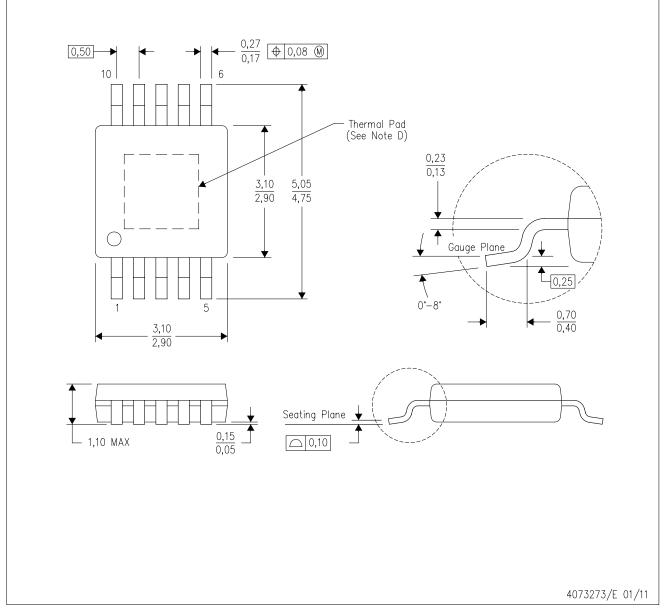

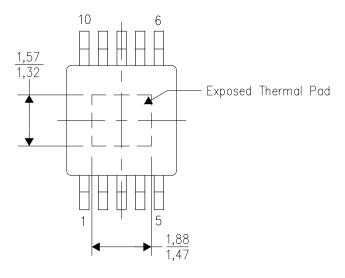

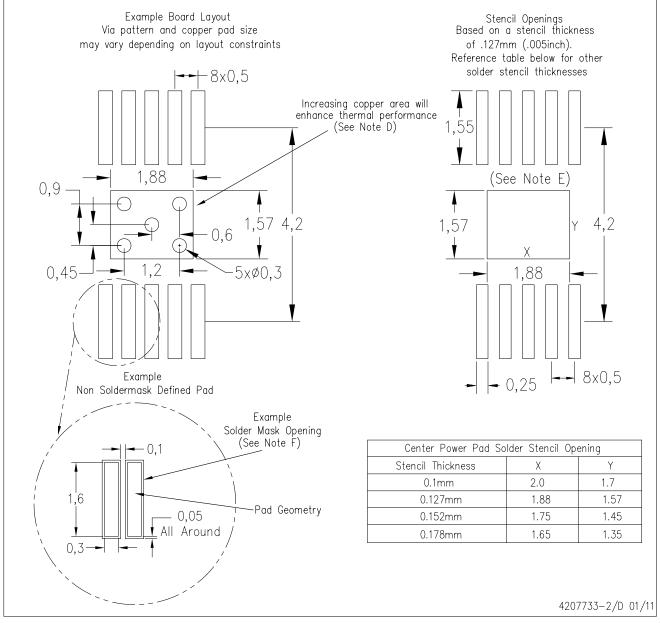

## **DEVICE INFORMATION**

## **PIN CONFIGURATION**

## DGQ PowerPAD PACKAGE (Top View)

## **PIN FUNCTIONS**

| PIN         |     |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|-------------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME        | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| воот        | 1   | 0   | A bootstrap capacitor is required between BOOT and PH. If the voltage on this capacitor is below the minimum required by the output device, the output is forced to switch off until the capacitor is refreshed.                                                                                                                                                                                                                                                                                              |  |  |  |

| СОМР        | 8   | 0   | Error amplifier output, and input to the output switch current comparator. Connect frequency compensation components to this pin.                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| EN          | 3   | ı   | Enable pin, internal pull-up current source. Pull below 1.2 V to disable. Float to enable. Adjust the input undervoltage lockout with two resistors.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| GND         | 9   | -   | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| PH          | 10  | I   | The source of the internal high-side power MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Thermal Pad | 11  | -   | GND pin must be electrically connected to the exposed pad on the printed circuit board for proper operation.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| PWRGD       | 6   | 0   | An open drain output, asserts low if output voltage is low due to thermal shutdown, dropout, over-voltage or EN shut down.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| RT/CLK      | 5   | I   | Resistor Timing and External Clock. An internal amplifier holds this pin at a fixed voltage when using an external resistor to ground to set the switching frequency. If the pin is pulled above the PLL upper threshold, a mode change occurs and the pin becomes a synchronization input. The internal amplifier is disabled and the pin is a high impedance clock input to the internal PLL. If clocking edges stop, the internal amplifier is re-enabled and the mode returns to a resistor set function. |  |  |  |

| SS/TR       | 4   | I   | Slow-start and Tracking. An external capacitor connected to this pin sets the output rise time. Since the voltage on this pin overrides the internal reference, it can be used for tracking and sequencing.                                                                                                                                                                                                                                                                                                   |  |  |  |

| VIN         | 2   | I   | Input supply voltage, 3.5 V to 60 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| VSENSE      | 7   | I   | Inverting node of the transconductance (g <sub>M</sub> ) error amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

Product Folder Link(s): TPS54160

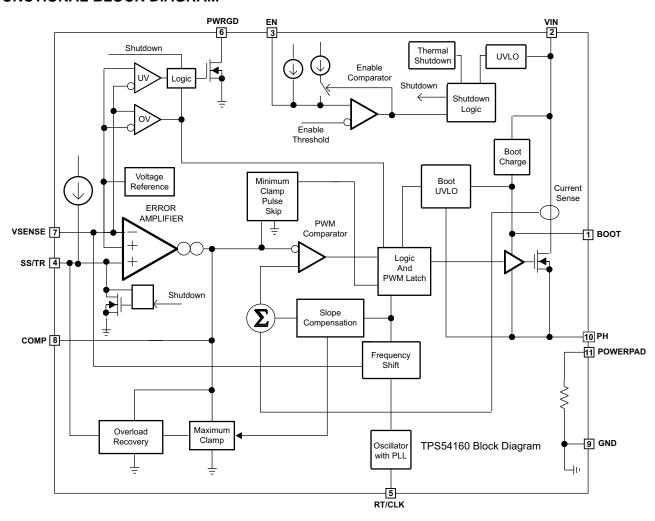

### **FUNCTIONAL BLOCK DIAGRAM**

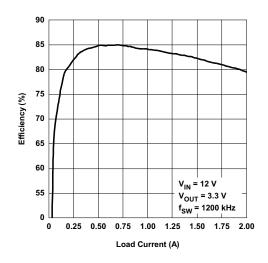

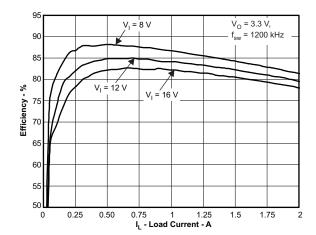

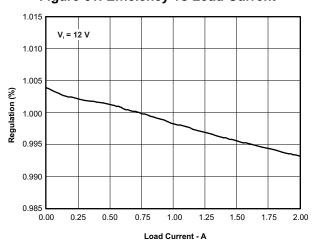

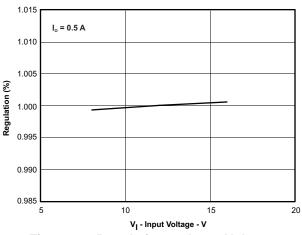

### **TYPICAL CHARACTERISTICS**

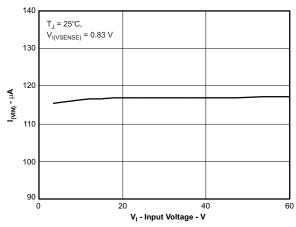

## ON RESISTANCE vs JUNCTION TEMPERATURE

**VOLTAGE REFERENCE vs JUNCTION TEMPERATURE**

Figure 2.

#### SWITCH CURRENT LIMIT vs JUNCTION TEMPERATURE

**SWITCHING FREQUENCY vs JUNCTION TEMPERATURE**

Figure 4.

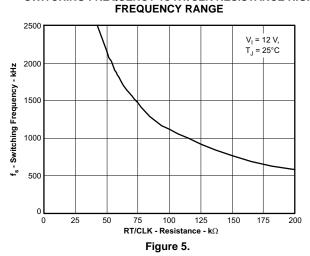

## SWITCHING FREQUENCY vs RT/CLK RESISTANCE HIGH

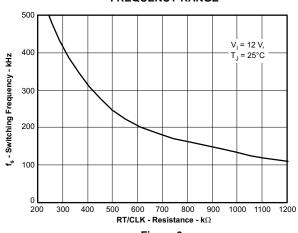

#### SWITCHING FREQUENCY vs RT/CLK RESISTANCE LOW FREQUENCY RANGE

Figure 6.

## **TYPICAL CHARACTERISTICS (continued)**

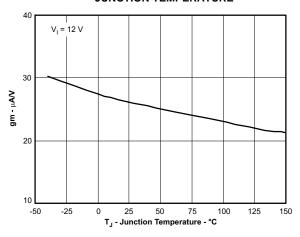

#### EA TRANSCONDUCTANCE DURING SLOW START vs JUNCTION TEMPERATURE

Figure 7.

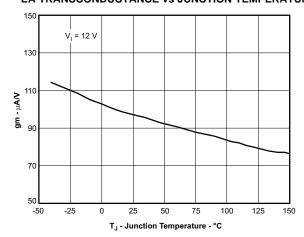

#### EA TRANSCONDUCTANCE vs JUNCTION TEMPERATURE

Figure 8.

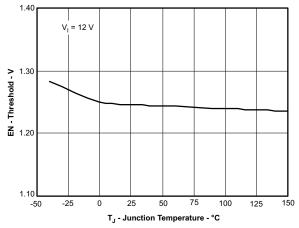

#### **EN PIN VOLTAGE vs JUNCTION TEMPERATURE**

Figure 9.

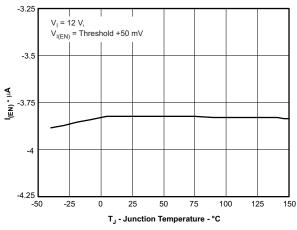

#### **EN PIN CURRENT vs JUNCTION TEMPERATURE**

Figure 10.

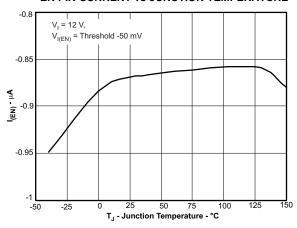

#### **EN PIN CURRENT vs JUNCTION TEMPERATURE**

Figure 11.

#### SS/TR CHARGE CURRENT vs JUNCTION TEMPERATURE

Figure 12.

## **TYPICAL CHARACTERISTICS (continued)**

## SS/TR DISCHARGE CURRENT vs JUNCTION TEMPERATURE

Figure 13.

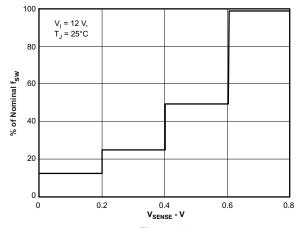

#### **SWITCHING FREQUENCY vs VSENSE**

Figure 14.

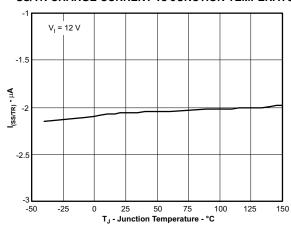

## SHUTDOWN SUPPLY CURRENT vs JUNCTION TEMPERATURE

Figure 15.

### SHUTDOWN SUPPLY CURRENT vs INPUT VOLTAGE (Vin)

Figure 16.

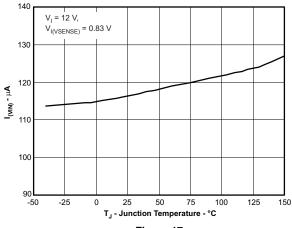

## VIN SUPPLY CURRENT vs JUNCTION TEMPERATURE

Figure 17.

## VIN SUPPLY CURRENT vs INPUT VOLTAGE

Figure 18.

## **TYPICAL CHARACTERISTICS (continued)**

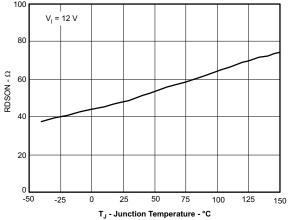

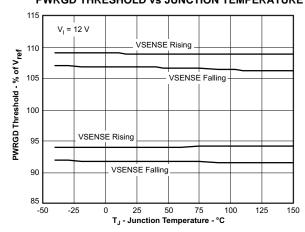

#### **PWRGD ON RESISTANCE vs JUNCTION TEMPERATURE**

Figure 19.

## PWRGD THRESHOLD vs JUNCTION TEMPERATURE

Figure 20.

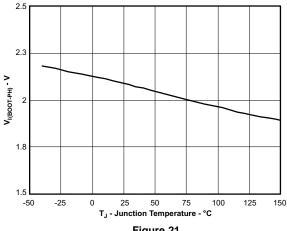

### **BOOT-PH UVLO vs JUNCTION TEMPERATURE**

Figure 21.

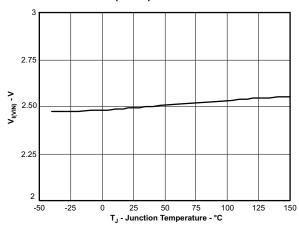

## INPUT VOLTAGE (UVLO) vs JUNCTION TEMPERATURE

Figure 22.

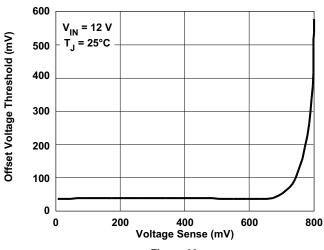

## SS/TR TO VSENSE OFFSET vs VSENSE

Figure 23.

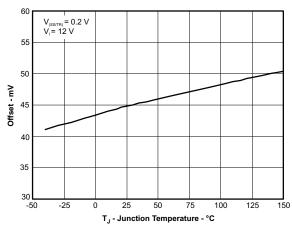

#### SS/TR TO VSENSE OFFSET vs TEMPERATURE

Figure 24.

#### OVERVIEW

The TPS54160 device is a 60-V, 1.5-A, step-down (buck) regulator with an integrated high-side n-channel MOSFET. To improve performance during line and load transients the device implements a constant frequency. current mode control which reduces output capacitance and simplifies external frequency compensation design. The wide switching frequency of 100kHz to 2500kHz allows for efficiency and size optimization when selecting the output filter components. The switching frequency is adjusted using a resistor to ground on the RT/CLK pin. The device has an internal phase lock loop (PLL) on the RT/CLK pin that is used to synchronize the power switch turn on to a falling edge of an external system clock.

The TPS54160 has a default start up voltage of approximately 2.5V. The EN pin has an internal pull-up current source that can be used to adjust the input voltage under voltage lockout (UVLO) threshold with two external resistors. In addition, the pull up current provides a default condition. When the EN pin is floating the device operates. The operating current is 116 µA when not switching and under no load. When the device is disabled, the supply current is 1.3 µA.

The integrated 200mΩ high-side MOSFET allows for high efficiency power supply designs capable of delivering 1.5 A of continuous current to a load. The TPS54160 reduces the external component count by integrating the boot recharge diode. The bias voltage for the integrated high-side MOSFET is supplied by a capacitor on the BOOT to PH pin. The boot capacitor voltage is monitored by an UVLO circuit and turns on the high-side MOSFET off when the boot voltage falls below a preset threshold. The TPS54160 can operate at high duty cycles because of the boot UVLO. The output voltage can be stepped down to as low as the 0.8V reference.

The TPS54160 has a power good comparator (PWRGD) which asserts when the regulated output voltage is less than 92% or greater than 109% of the nominal output voltage. The PWRGD pin is an open drain output which deasserts when the VSENSE pin voltage is between 94% and 107% of the nominal output voltage allowing the pin to transition high when a pull-up resistor is used.

The TPS54160 minimizes excessive output overvoltage (OV) transients by taking advantage of the OV power good comparator. When the OV comparator is activated, the high-side MOSFET is turned off and masked from turning on until the output voltage is lower than 107%.

The SS/TR (slow start/tracking) pin is used to minimize inrush currents or provide power supply sequencing during power up. A small value capacitor should be coupled to the pin to adjust the slow start time. A resistor divider can be coupled to the pin for critical power supply sequencing requirements. The SS/TR pin is discharged before the output powers up. This discharging ensures a repeatable restart after an over-temperature fault, UVLO fault or a disabled condition.

The TPS54160, also, discharges the slow start capacitor during overload conditions with an overload recovery circuit. The overload recovery circuit will slow start the output from the fault voltage to the nominal regulation voltage once a fault condition is removed. A frequency foldback circuit reduces the switching frequency during startup and overcurrent fault conditions to help control the inductor current.

Product Folder Link(s): TPS54160

#### DETAILED DESCRIPTION

## **Fixed Frequency PWM Control**

The TPS54160 uses an adjustable fixed frequency, peak current mode control. The output voltage is compared through external resistors on the VSENSE pin to an internal voltage reference by an error amplifier which drives the COMP pin. An internal oscillator initiates the turn on of the high-side power switch. The error amplifier output is compared to the high-side power switch current. When the power switch current reaches the level set by the COMP voltage, the power switch is turned off. The COMP pin voltage will increase and decrease as the output current increases and decreases. The device implements a current limit by clamping the COMP pin voltage to a maximum level. The Eco-Mode<sup>TM</sup> is implemented with a minimum clamp on the COMP pin.

## **Slope Compensation Output Current**

The TPS54160 adds a compensating ramp to the switch current signal. This slope compensation prevents sub-harmonic oscillations. The available peak inductor current remains constant over the full duty cycle range.

### **Pulse Skip Eco-Mode**

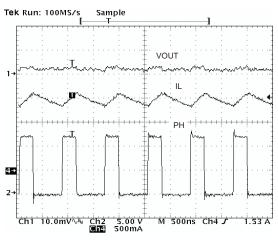

The TPS54160 operates in a pulse skip Eco mode at light load currents to improve efficiency by reducing switching and gate drive losses. The TPS54160 is designed so that if the output voltage is within regulation and the peak switch current at the end of any switching cycle is below the pulse skipping current threshold, the device enters Eco mode. This current threshold is the current level corresponding to a nominal COMP voltage or 500mV.

When in Eco-mode, the COMP pin voltage is clamped at 500mV and the high-side MOSFET is inhibited. Further decreases in load current or in output voltage can not drive the COMP pin below this clamp voltage level.

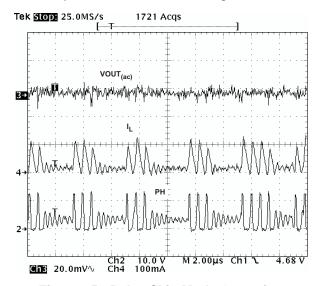

Since the device is not switching, the output voltage begins to decay. As the voltage control loop compensates for the falling output voltage, the COMP pin voltage begins to rise. At this time, the high-side MOSFET is enabled and a switching pulse initiates on the next switching cycle. The peak current is set by the COMP pin voltage. The output voltage re-charges the regulated value (see Figure 25), then the peak switch current starts to decrease, and eventually falls below the Eco mode threshold at which time the device again enters Eco mode.

For Eco mode operation, the TPS54160 senses peak current, not average or load current, so the load current where the device enters Eco mode is dependent on the output inductor value. For example, the circuit in Figure 51 enters Eco mode at about 18mA of output current. When the load current is low and the output voltage is within regulation, the device enters a sleep mod,e and draws only  $116\mu$ A input quiescent current. The internal PLL remains operating when in sleep mode. When operating at light load currents in the pulse skip mode, the switching transitions occur synchronously with the external clock signal.

Figure 25. Pulse Skip Mode Operation

## **Low Dropout Operation and Bootstrap Voltage (BOOT)**

The TPS54160 has an integrated boot regulator, and requires a small ceramic capacitor between the BOOT and PH pins to provide the gate drive voltage for the high-side MOSFET. The BOOT capacitor is refreshed when the high-side MOSFET is off and the low-side diode conducts. The value of this ceramic capacitor should be  $0.1\mu$ F. A ceramic capacitor with an X7R or X5R grade dielectric with a voltage rating of 10V or higher is recommended because of the stable characteristics overtemperature and voltage.

To improve drop out, the TPS54160 is designed to operate at 100% duty cycle as long as the BOOT to PH pin voltage is greater than 2.1V. When the voltage from BOOT to PH drops below 2.1V, the high-side MOSFET is turned off using an UVLO circuit which allows the low-side diode to conduct and refresh the charge on the BOOT capacitor. Since the supply current sourced from the BOOT capacitor is low, the high-side MOSFET can remain on for more switching cycles than are required to refresh the capacitor, thus the effective duty cycle of the switching regulator is high.

The effective duty cycle during dropout of the regulator is mainly influenced by the voltage drops across the power MOSFET, inductor resistance, low-side diode and printed circuit board resistance. During operating conditions in which the input voltage drops and the regulator is operating in continuous conduction mode, the high-side MOSFET can remain on for 100% of the duty cycle to maintain output regulation, until the BOOT to PH voltage falls below 2.1V.

Attention must be taken in maximum duty cycle applications which experience extended time periods with light loads or no load. When the voltage across the BOOT capacitor falls below the 2.1V UVLO threshold, the high-side MOSFET is turned off, but there may not be enough inductor current to pull the PH pin down to recharge the BOOT capacitor. The high-side MOSFET of the regulator stops switching because the voltage across the BOOT capacitor is less than 2.1V. The output capacitor then decays until the difference in the input voltage and output voltage is greater than 2.1V, at which point the BOOT UVLO threshold is exceeded, and the device starts switching again until the desired output voltage is reached. This operating condition persists until the input voltage and/or the load current increases. It is recommended to adjust the VIN stop voltage greater than the BOOT UVLO trigger condition at the minimum load of the application using the adjustable VIN UVLO feature with resistors on the EN pin.

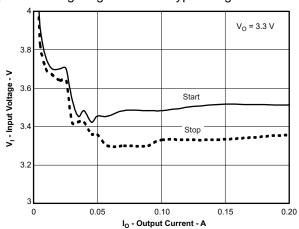

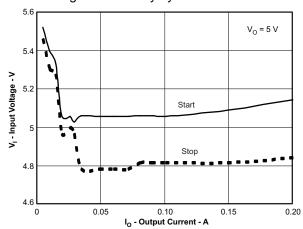

The start and stop voltages for typical 3.3V and 5V output applications are shown in Figure 26 and Figure 27. The voltages are plotted versus load current. The start voltage is defined as the input voltage needed to regulate the output within 1%. The stop voltage is defined as the input voltage at which the output drops by 5% or stops switching.

During high duty cycle conditions, the inductor current ripple increases while the BOOT capacitor is being recharged resulting in an increase in ripple voltage on the output. This is due to the recharge time of the boot capacitor being longer than the typical high-side off time when switching occurs every cycle.

Figure 26. 3.3V Start/Stop Voltage

Figure 27. 5.0V Start/Stop Voltage

## **Error Amplifier**

The TPS54160 has a transconductance amplifier for the error amplifier. The error amplifier compares the VSENSE voltage to the lower of the SS/TR pin voltage or the internal 0.8-V voltage reference. The transconductance ( $g_M$ ) of the error amplifier is  $97\mu$ A/V during normal operation. During the slow start operation, the transconductance is a fraction of the normal operating transconductance. When the voltage of the VSENSE pin is below 0.8 V and the device is regulating using the SS/TR voltage, the transconductance is 25  $\mu$ A/V.

The frequency compensation components (capacitor, series resistor and capacitor) are added to the COMP pin to ground.

## Voltage Reference

The voltage reference system produces a precise ±2% voltage reference over temperature by scaling the output of a temperature stable bandgap circuit.

## **Adjusting the Output Voltage**

The output voltage is set with a resistor divider from the output node to the VSENSE pin. It is recommended to use 1% tolerance or better divider resistors. Start with a 10 k $\Omega$  for the R2 resistor and use the Equation 1 to calculate R1. To improve efficiency at light loads consider using larger value resistors. If the values are too high, the regulator becomes more susceptible to noise and voltage errors from the VSENSE input current are noticeable.

$$R1 = R2 \times \left(\frac{\left(V_{OUT} - 0.8 V\right)}{0.8 V}\right)$$

(1)

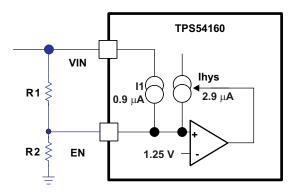

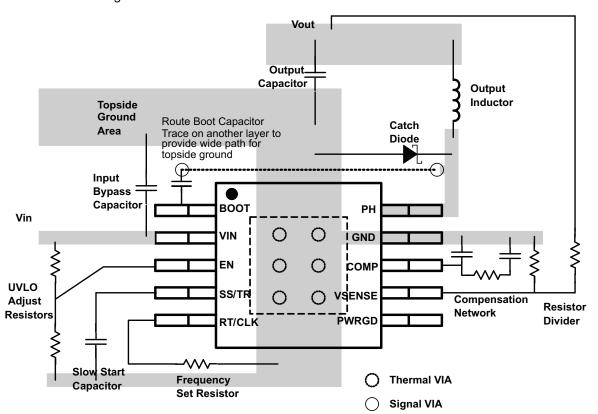

## **Enable and Adjusting Undervoltage Lockout**

The TPS54160 is disabled when the VIN pin voltage falls below 2.5 V. If an application requires a higher undervoltage lockout (UVLO), use the EN pin as shown in Figure 28 to adjust the input voltage UVLO by using the two external resistors. Though it is not necessary to use the UVLO adjust registers, for operation it is highly recommended to provide consistent power up behavior. The EN pin has an internal pull-up current source, I1, of  $0.9\mu$ A that provides the default condition of the TPS54160 operating when the EN pin floats. Once the EN pin voltage exceeds 1.25V, an additional 2.9  $\mu$ A of hysteresis, lhys, is added. This additional current facilitates input voltage hysteresis. Use Equation 2 to set the external hysteresis for the input voltage. Use Equation 3 to set the input start voltage.

Figure 28. Adjustable Undervoltage Lockout (UVLO)

$$R1 = \frac{V_{START} - V_{STOP}}{I_{HYS}}$$

$$R2 = \frac{V_{ENA}}{\frac{V_{START} - V_{ENA}}{R1} + I_{1}}$$

(2)

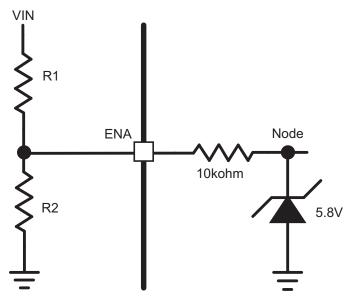

Another technique to add input voltage hysteresis is shown in Figure 29. This method may be used, if the resistance values are high from the previous method and a wider voltage hysteresis is needed. The resistor R3 sources additional hysteresis current into the EN pin.

Figure 29. Adding Additional Hysteresis

$$R1 = \frac{V_{START} - V_{OUT}}{I_{HYS} + \frac{V_{OUT}}{R3}}$$

$$R2 = \frac{V_{ENA}}{\frac{V_{START} - V_{ENA}}{R1} + I_1 - \frac{V_{ENA}}{R3}}$$

(4)

Do not place a low-impedance voltage source with greater than 5 V directly on the EN pin. Do not place a capacitor directly on the EN pin if V<sub>EN</sub> > 5 V when using a voltage divider to adjust the start and stop voltage. The node voltage, (see Figure 30) must remain equal to or less than 5.8 V. The zener diode can sink up to 100 μA. The EN pin voltage can be greater than 5 V if the V<sub>IN</sub> voltage source has a high impedance and does not source more than 100 µA into the EN pin.

Figure 30. Node Voltage

Copyright © 2008-2010, Texas Instruments Incorporated

Submit Documentation Feedback

(5)

## Slow Start/Tracking Pin (SS/TR)

The TPS54160 effectively uses the lower voltage of the internal voltage reference or the SS/TR pin voltage as the power-supply's reference voltage and regulates the output accordingly. A capacitor on the SS/TR pin to ground implements a slow start time. The TPS54160 has an internal pull-up current source of  $2\mu$ A that charges the external slow start capacitor. The calculations for the slow start time (10% to 90%) are shown in Equation 6. The voltage reference ( $V_{REF}$ ) is 0.8 V and the slow start current ( $I_{SS}$ ) is  $2\mu$ A. The slow start capacitor should remain lower than  $0.47\mu$ F and greater than 0.47nF.

$$C_{SS}(nF) = \frac{t_{SS}(ms) \times I_{SS}(\mu A)}{V_{REF}(V) \times 0.8}$$

(6)

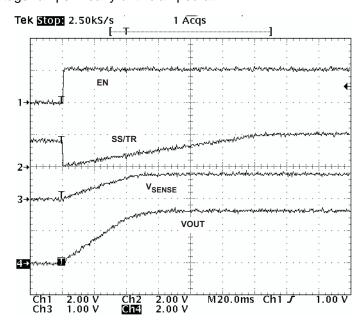

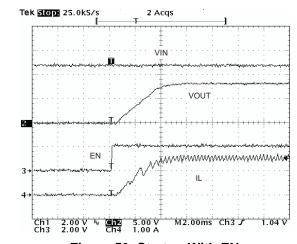

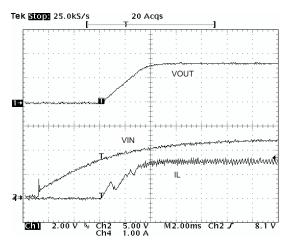

At power up, the TPS54160 does not start switching until the slow start pin is discharged to less than 40 mV to ensure a proper power up, see Figure 31.

Also, during normal operation, the TPS54160 stops switching and the SS/TR must be discharged to 40 mV, when the VIN UVLO is exceeded, EN pin pulled below 1.25V, or a thermal shutdown event occurs.

The VSENSE voltage follows the SS/TR pin voltage with a 45mV offset up to 85% of the internal voltage reference. When the SS/TR voltage is greater than 85% on the internal reference voltage the offset increases as the effective system reference transitions from the SS/TR voltage to the internal voltage reference (see Figure 23). The SS/TR voltage ramps linearly until clamped at 1.7V.

Figure 31. Operation of SS/TR Pin when Starting

#### **Overload Recovery Circuit**

The TPS54160 has an overload recovery (OLR) circuit. The OLR circuit slow starts the output from the overload voltage to the nominal regulation voltage once the fault condition is removed. The OLR circuit discharges the SS/TR pin to a voltage slightly greater than the VSENSE pin voltage using an internal pull down of 100  $\mu$ A when the error amplifier is changed to a high voltage from a fault condition. When the fault condition is removed, the output slow-starts from the fault voltage to nominal output voltage.

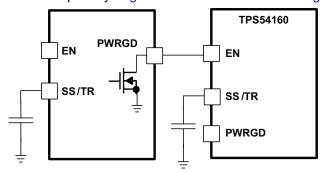

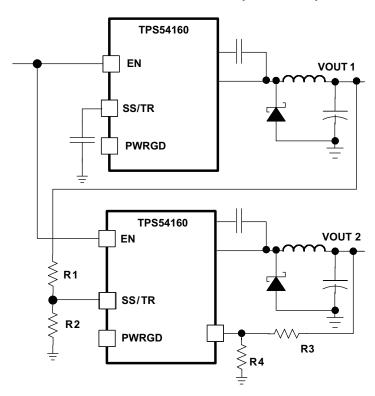

## Sequencing

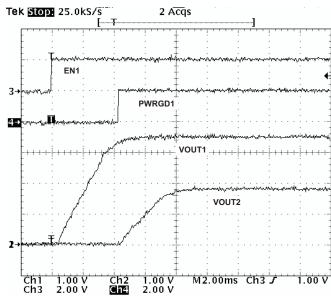

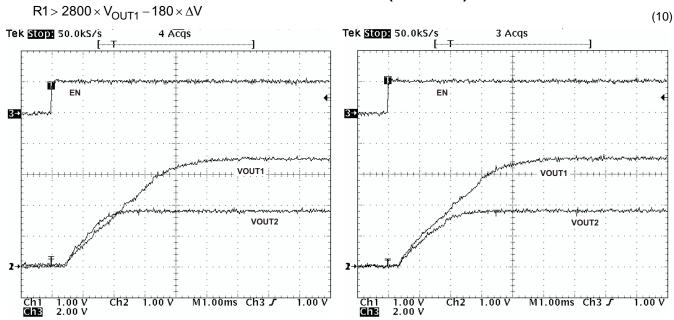

Many of the common power supply sequencing methods can be implemented using the SS/TR, EN and PWRGD pins. The sequential method can be implemented using an open drain output of a power on reset pin of another device. The sequential method is illustrated in Figure 32 using two TPS54160 devices. The power good is coupled to the EN pin on the TPS54160 which enables the second power supply once the primary supply reaches regulation. If needed, a 1nF ceramic capacitor on the EN pin of the second power supply provides a 1-ms start-up delay. Figure 33 shows the results of Figure 32.

Figure 32. Schematic for Sequential Start-Up Sequence

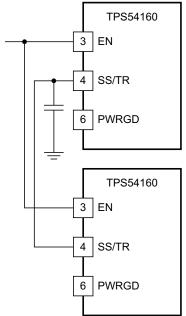

Figure 35. Ratio-Metric Startup using Coupled SS/TR pins

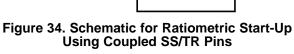

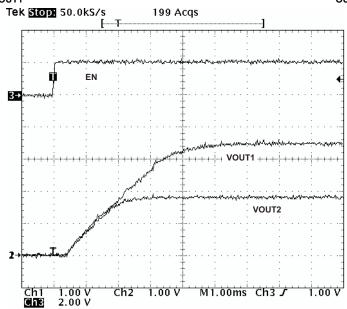

Figure 34 shows a method for ratio-metric start up sequence by connecting the SS/TR pins together. The regulator outputs ramp up to reach regulation at the same time. When calculating the slow start time the pull up current source must be doubled in Equation 6. Figure 35 shows the results of Figure 34.

Figure 36. Schematic for Ratiometric and Simultaneous Start-Up Sequence

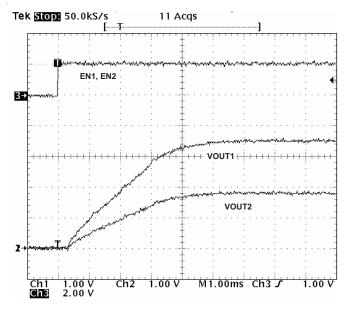

Ratio-metric and simultaneous power supply sequencing can be implemented by connecting the resistor network of R1 and R2 shown in Figure 36 to the output of the power supply that needs to be tracked or another voltage reference source. Using Equation 7 and Equation 8, the tracking resistors can be calculated to initiate the V<sub>OUT2</sub> slightly before, after or at the same time as V<sub>OUT1</sub>. Equation 9 is the voltage difference between V<sub>OUT1</sub> and V<sub>OUT2</sub> at the 95% of nominal output regulation.

The ΔV variable is zero volts for simultaneous sequencing. To minimize the effect of the inherent SS/TR to VSENSE offset (V<sub>SS(offset)</sub>) in the slow start circuit and the offset created by the pull-up current source (I<sub>SS</sub>) and tracking resistors, the  $V_{SS(offset)}$  and  $I_{SS}$  are included as variables in the equations.

To design a ratio-metric start up in which the  $V_{OUT2}$  voltage is slightly greater than the  $V_{OUT1}$  voltage when  $V_{OUT2}$  reaches regulation, use a negative number in Equation 7 through Equation 9 for  $\Delta V$ . Equation 9 results in a positive number for applications which the  $V_{OUT2}$  is slightly lower than  $V_{OUT1}$  when  $V_{OUT2}$  regulation is achieved.

Since the SS/TR pin must be pulled below 40 mV before starting after an EN, UVLO or thermal shutdown fault, careful selection of the tracking resistors is needed to ensure the device restarts after a fault. Make sure the calculated R1 value from Equation 7 is greater than the value calculated in Equation 10 to ensure the device can recover from a fault.

As the SS/TR voltage becomes more than 85% of the nominal reference voltage the V<sub>SS(offset)</sub> becomes larger as the slow start circuits gradually handoff the regulation reference to the internal voltage reference. The SS/TR pin voltage needs to be greater than 1.3 V for a complete handoff to the internal voltage reference as shown in Figure 23.

$$R1 = \frac{V_{OUT2} + \Delta V}{V_{REF}} + \frac{V_{SS(offset)}}{I_{SS}}$$

$$R2 = \frac{V_{REF} \times R1}{V_{OUT2} + \Delta V - V_{REF}}$$

(8)

$$R2 = \frac{V_{REF} \times IVI}{V_{OUT2} + \Delta V - V_{REF}}$$

(8)

$$\Delta V = V_{OUT1} - V_{OUT2} \tag{9}$$

Figure 37. Ratiometric Startup with  $V_{\text{OUT2}}$  Leading  $V_{\text{OUT1}}$

Figure 38. Ratiometric Startup with  $V_{\text{OUT1}}$  Leading  $V_{\text{OUT2}}$

Figure 39. Simultaneous Startup With Tracking Resistor

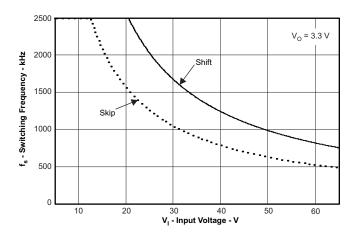

f<sub>s</sub> - Switching Frequency - kHz

25

## **DETAILED DESCRIPTION (continued)**

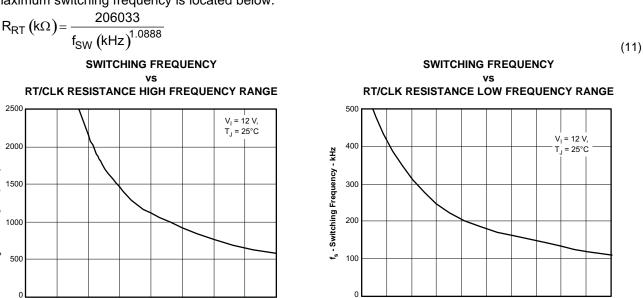

## **Constant Switching Frequency and Timing Resistor (RT/CLK Pin)**

The switching frequency of the TPS54160 is adjustable over a wide range from approximately 100kHz to 2500kHz by placing a resistor on the RT/CLK pin. The RT/CLK pin voltage is typically 0.5V and must have a resistor to ground to set the switching frequency. To determine the timing resistance for a given switching frequency, use Equation 11 or the curves in Figure 40 or Figure 41. To reduce the solution size one would typically set the switching frequency as high as possible, but tradeoffs of the supply efficiency, maximum input voltage and minimum controllable on time should be considered.

The minimum controllable on time is typically 130ns and limits the maximum operating input voltage.

The maximum switching frequency is also limited by the frequency shift circuit. More discussion on the details of the maximum switching frequency is located below.

Figure 40. High Range Timing Resistance

100

RT/CLK - Clock Resistance - kΩ

125

150

Figure 41. Low Range RT

500 600 700 800 900

RT/CLK - Resistance - kΩ

1000 1100 1200

300 400

200

### **Overcurrent Protection and Frequency Shift**

75

The TPS54160 implements current mode control which uses the COMP pin voltage to turn off the high-side MOSFET on a cycle by cycle basis. Each cycle the switch current and COMP pin voltage are compared, when the peak switch current intersects the COMP voltage, the high-side switch is turned off. During overcurrent conditions that pull the output voltage low, the error amplifier responds by driving the COMP pin high, increasing the switch current. The error amplifier output is clamped internally, which functions as a switch current limit.

To increase the maximum operating switching frequency at high input voltages the TPS54160 implements a frequency shift. The switching frequency is divided by 8, 4, 2, and 1 as the voltage ramps from 0 to 0.8 volts on VSENSE pin.

The device implements a digital frequency shift to enable synchronizing to an external clock during normal startup and fault conditions. Since the device can only divide the switching frequency by 8, there is a maximum input voltage limit in which the device operates and still have frequency shift protection.

During short-circuit events (particularly with high input voltage applications), the control loop has a finite minimum controllable on time and the output has a low voltage. During the switch on time, the inductor current ramps to the peak current limit because of the high input voltage and minimum on time. During the switch off time, the inductor would normally not have enough off time and output voltage for the inductor to ramp down by the ramp up amount. The frequency shift effectively increases the off time allowing the current to ramp down.

## **Selecting the Switching Frequency**

The switching frequency that is selected should be the lower value of the two equations, Equation 12 and Equation 13. Equation 12 is the maximum switching frequency limitation set by the minimum controllable on time. Setting the switching frequency above this value causes the regulator to skip switching pulses.

Equation 13 is the maximum switching frequency limit set by the frequency shift protection. To have adequate output short circuit protection at high input voltages, the switching frequency should be set to be less than the  $f_{SW(maxshift)}$  frequency. In Equation 13, to calculate the maximum switching frequency, consider that the output voltage decreases from the nominal voltage to 0 V, the  $f_{DIV}$  integer increases from 1 to 8 corresponding to the frequency shift.

In Figure 42, the solid line illustrates a typical safe operating area regarding frequency shift and assumes the output voltage is 0 V, and the resistance of the inductor is  $0.1\Omega$ , FET on-resistance of  $0.2\Omega$  and the diode voltage drop is 0.5 V. The dashed line is the maximum switching frequency to avoid pulse skipping. Enter these equations in a spreadsheet or other software or use the SwitcherPro design software to determine the switching frequency.

$$f_{SW(max\,skip)} = \frac{1}{t_{ON}} \times \left( \frac{I_L \times R_{dc} + V_{OUT} + V_d}{V_{IN} - I_L \times R_{DS(on)} + V_d} \right)$$

(12)

$$f_{SWshift} = \frac{f_{DIV}}{t_{ON}} \times \left( \frac{I_L \times R_{dc} + V_{OUT(sc)} + V_d}{V_{IN} - I_L \times R_{DS(on)} + V_d} \right)$$

(13)

$\begin{array}{ll} I_L & \text{inductor current} \\ R_{dc} & \text{inductor resistance} \\ V_{IN} & \text{maximum input voltage} \end{array}$

V<sub>OUT</sub> output voltage

V<sub>OUT(sc)</sub> output voltage during short

$\begin{array}{ll} \text{Vd} & \text{diode voltage drop} \\ \text{R}_{\text{DS(on)}} & \text{switch on resistance} \\ \text{t}_{\text{ON}} & \text{controllable on time} \\ \end{array}$

f<sub>DIV</sub> frequency divide equals (1, 2, 4, or 8)

Figure 42. Maximum Switching Frequency vs. Input Voltage

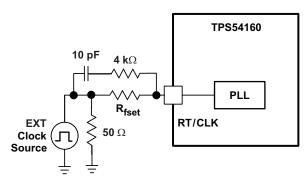

#### How to Interface to RT/CLK Pin

The RT/CLK pin can be used to synchronize the regulator to an external system clock. To implement the synchronization feature connect a square wave to the RT/CLK pin through the circuit network shown in Figure 43. The square wave amplitude must transition lower than 0.5V and higher than 2.2V on the RT/CLK pin and have an on time greater than 40 ns and an off time greater than 40 ns. The synchronization frequency range is 100 kHz to 2200 kHz. The rising edge of the PH is synchronized to the falling edge of RT/CLK pin signal. The external synchronization circuit should be designed in such a way that the device has the default frequency set resistor connected from the RT/CLK pin to ground should the synchronization signal turn off. It is recommended to use a frequency set resistor connected as shown in Figure 43 through a  $50\Omega$  resistor to ground. The resistor should set the switching frequency close to the external CLK frequency. It is recommended to ac couple the synchronization signal through a 10 pF ceramic capacitor to RT/CLK pin and a  $4k\Omega$  series resistor. The series resistor reduces PH jitter in heavy load applications when synchronizing to an external clock and in applications which transition from synchronizing to RT mode. The first time the CLK is pulled above the CLK threshold the device switches from the RT resistor frequency to PLL mode. The internal 0.5V voltage source is removed and the CLK pin becomes high impedance as the PLL starts to lock onto the external signal. Since there is a PLL on the regulator the switching frequency can be higher or lower than the frequency set with the external resistor. The device transitions from the resistor mode to the PLL mode and then will increase or decrease the switching frequency until the PLL locks onto the CLK frequency within 100 microseconds.

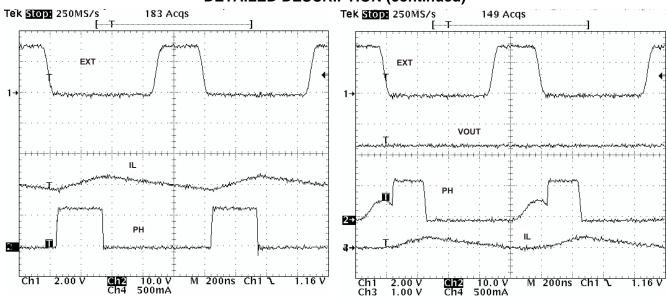

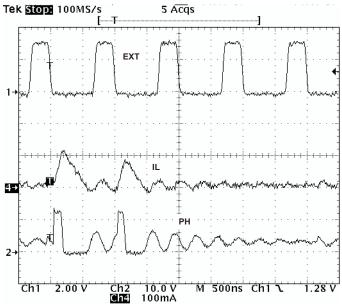

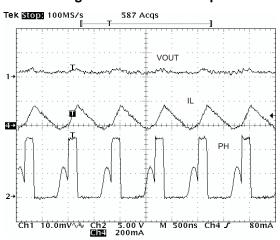

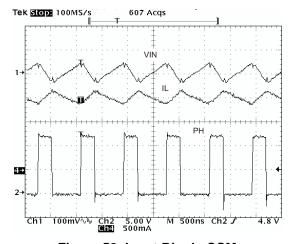

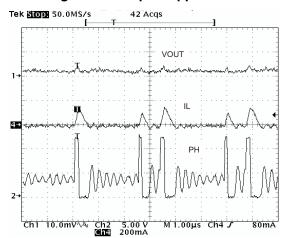

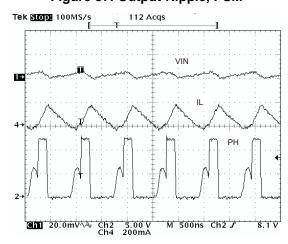

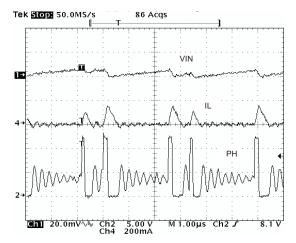

When the device transitions from the PLL to resistor mode the switching frequency will slow down from the CLK frequency to 150 kHz, then reapply the 0.5V voltage and the resistor will then set the switching frequency. The switching frequency is divided by 8, 4, 2, and 1 as the voltage ramps from 0 to 0.8 volts on VSENSE pin. The device implements a digital frequency shift to enable synchronizing to an external clock during normal startup and fault conditions. Figure 44, Figure 45 and Figure 46 show the device synchronized to an external system clock in continuous conduction mode (ccm) discontinuous conduction (dcm) and pulse skip mode (psm).

Figure 43. Synchronizing to a System Clock

Figure 44. Plot of Synchronizing in ccm

Figure 45. Plot of Synchronizing in dcm

Figure 46. Plot of Synchronizing in PSM

## **Power Good (PWRGD Pin)**

The PWRGD pin is an open drain output. Once the VSENSE pin is between 94% and 107% of the internal voltage reference the PWRGD pin is de-asserted and the pin floats. It is recommended to use a pull-up resistor between the values of 10 and  $100k\Omega$  to a voltage source that is 5.5V or less. The PWRGD is in a defined state once the VIN input voltage is greater than 1.5V but with reduced current sinking capability. The PWRGD will achieve full current sinking capability as VIN input voltage approaches 3V.

The PWRGD pin is pulled low when the VSENSE is lower than 92% or greater than 109% of the nominal internal reference voltage. Also, the PWRGD is pulled low, if the UVLO or thermal shutdown are asserted or the EN pin pulled low.

## **Overvoltage Transient Protection**

The TPS54160 incorporates an overvoltage transient protection (OVTP) circuit to minimize voltage overshoot when recovering from output fault conditions or strong unload transients on power supply designs with low value output capacitance. For example, when the power supply output is overloaded the error amplifier compares the actual output voltage to the internal reference voltage. If the VSENSE pin voltage is lower than the internal reference voltage for a considerable time, the output of the error amplifier will respond by clamping the error amplifier output to a high voltage. Thus, requesting the maximum output current. Once the condition is removed, the regulator output rises and the error amplifier output transitions to the steady state duty cycle. In some applications, the power supply output voltage can respond faster than the error amplifier output can respond, this actuality leads to the possibility of an output overshoot. The OVTP feature minimizes the output overshoot, when using a low value output capacitor, by implementing a circuit to compare the VSENSE pin voltage to OVTP threshold which is 109% of the internal voltage reference. If the VSENSE pin voltage is greater than the OVTP threshold, the high-side MOSFET is disabled preventing current from flowing to the output and minimizing output overshoot. When the VSENSE voltage drops lower than the OVTP threshold, the high-side MOSFET is allowed to turn on at the next clock cycle.

#### **Thermal Shutdown**

The device implements an internal thermal shutdown to protect itself if the junction temperature exceeds 182°C. The thermal shutdown forces the device to stop switching when the junction temperature exceeds the thermal trip threshold. Once the die temperature decreases below 182°C, the device reinitiates the power up sequence by discharging the SS/TR pin.

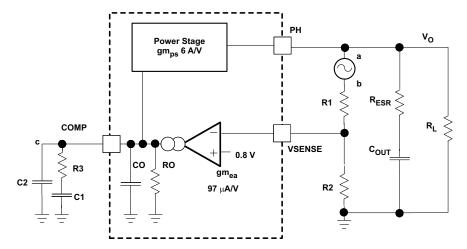

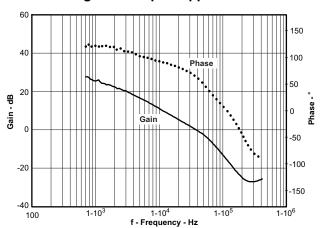

#### **Small Signal Model for Loop Response**

Figure 47 shows an equivalent model for the TPS54160 control loop which can be modeled in a circuit simulation program to check frequency response and dynamic load response. The error amplifier is a transconductance amplifier with a  $gm_{EA}$  of 97  $\mu$ A/V. The error amplifier can be modeled using an ideal voltage controlled current source. The resistor  $R_o$  and capacitor  $C_o$  model the open loop gain and frequency response of the amplifier. The 1mV ac voltage source between the nodes a and b effectively breaks the control loop for the frequency response measurements. Plotting c/a shows the small signal response of the frequency compensation. Plotting a/b shows the small signal response of the overall loop. The dynamic loop response can be checked by replacing  $R_L$  with a current source with the appropriate load step amplitude and step rate in a time domain analysis. This equivalent model is only valid for continuous conduction mode designs.

Figure 47. Small Signal Model for Loop Response

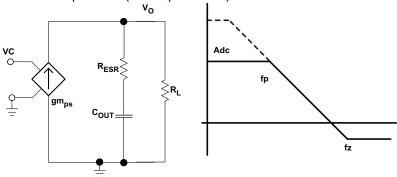

#### Simple Small Signal Model for Peak Current Mode Control

Figure 48 describes a simple small signal model that can be used to understand how to design the frequency compensation. The TPS54160 power stage can be approximated to a voltage-controlled current source (duty

cycle modulator) supplying current to the output capacitor and load resistor. The control to output transfer function is shown in Equation 14 and consists of a dc gain, one dominant pole, and one ESR zero. The quotient of the change in switch current and the change in COMP pin voltage (node c in Figure 47) is the power stage transconductance. The  $gm_{PS}$  for the TPS54160 is 6 A/V. The low-frequency gain of the power stage frequency response is the product of the transconductance and the load resistance as shown in Equation 15.

As the load current increases and decreases, the low-frequency gain decreases and increases, respectively. This variation with the load may seem problematic at first glance, but fortunately the dominant pole moves with the load current (see Equation 16). The combined effect is highlighted by the dashed line in the right half of Figure 48. As the load current decreases, the gain increases and the pole frequency lowers, keeping the 0-dB crossover frequency the same for the varying load conditions which makes it easier to design the frequency compensation. The type of output capacitor chosen determines whether the ESR zero has a profound effect on the frequency compensation design. Using high ESR aluminum electrolytic capacitors may reduce the number frequency compensation components needed to stabilize the overall loop because the phase margin increases from the ESR zero at the lower frequencies (see Equation 17).

Figure 48. Simple Small Signal Model and Frequency Response for Peak Current Mode Control

$$\frac{V_{OUT}}{V_{C}} = Adc \times \frac{\left(1 + \frac{s}{2\pi \times f_{Z}}\right)}{\left(1 + \frac{s}{2\pi \times f_{P}}\right)}$$

(14)

$$Adc = gm_{ps} \times R_{L}$$

(15)

$$f_{P} = \frac{1}{C_{OUT} \times R_{L} \times 2\pi} \tag{16}$$

$$f_{Z} = \frac{1}{C_{\text{OUT}} \times R_{\text{ESR}} \times 2\pi}$$

(17)

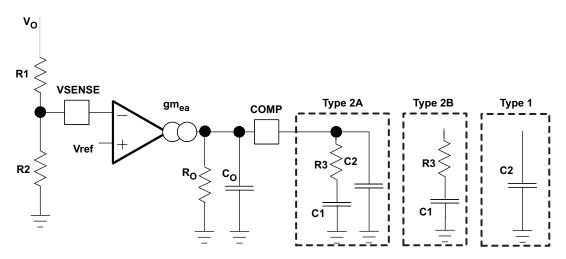

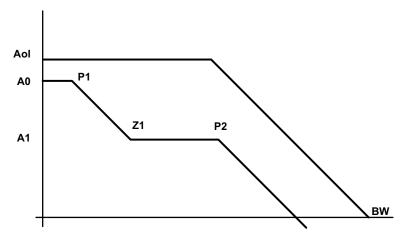

### **Small Signal Model for Frequency Compensation**

The TPS54160 uses a transconductance amplifier for the error amplifier and readily supports three of the commonly-used frequency compensation circuits. Compensation circuits Type 2A, Type 2B, and Type 1 are shown in Figure 49. Type 2 circuits most likely implemented in high bandwidth power-supply designs using low ESR output capacitors. The Type 1 circuit is used with power-supply designs with high-ESR aluminum electrolytic or tantalum capacitors.. Equation 18 and Equation 19 show how to relate the frequency response of the amplifier to the small signal model in Figure 49. The open-loop gain and bandwidth are modeled using the  $R_{\rm O}$  and  $C_{\rm O}$  shown in Figure 49. See the application section for a design example using a Type 2A network with a low ESR output capacitor.

Equation 18 through Equation 27 are provided as a reference for those who prefer to compensate using the preferred methods. Those who prefer to use prescribed method use the method outlined in the application section or use switched information.

Figure 49. Types of Frequency Compensation

Figure 50. Frequency Response of the Type 2A and Type 2B Frequency Compensation

$$Ro = \frac{Aol(V/V)}{gm_{ea}}$$

(18)

$$C_{OUT} = \frac{gm_{ea}}{2\pi \times BW (Hz)}$$

(19)

$$EA = A0 \times \frac{\left(1 + \frac{s}{2\pi \times f_{Z1}}\right)}{\left(1 + \frac{s}{2\pi \times f_{P1}}\right) \times \left(1 + \frac{s}{2\pi \times f_{P2}}\right)}$$

(20)

$$A0 = gm_{ea} \times Ro \times \frac{R2}{R1 + R2}$$

(21)

$$A1 = gm_{ea} \times Ro||R3 \times \frac{R2}{R1 + R2}$$

(22)

$$P1 = \frac{1}{2\pi \times Ro \times C1} \tag{23}$$

$$Z1 = \frac{1}{2\pi \times R3 \times C1} \tag{24}$$

P2 =

$$\frac{1}{2\pi \times R3 \mid |Ro \times (C2 + Co)|}$$

type 2a (25)

$$P2 = \frac{1}{2\pi \times R3 \mid \mid Ro \times Co} \text{ type 2b}$$

(26)

P2 =

$$\frac{1}{2\pi \times \text{Ro} \times (\text{C2 + Co})}$$

type 1 (27)

#### **APPLICATION INFORMATION**

## Design Guide — Step-By-Step Design Procedure

This example details the design of a high frequency switching regulator design using ceramic output capacitors. A few parameters must be known in order to start the design process. These parameters are typically determined at the system level. For this example, we will start with the following known parameters:

| Output Voltage                         | 3.3 V                  |

|----------------------------------------|------------------------|

| Transient Response 0 to 1.5A load step | ΔV <sub>OUT</sub> = 4% |

| Maximum Output Current                 | 1.5 A                  |

| Input Voltage                          | 12 V nom. 8 V to 18 V  |

| Output Voltage Ripple                  | $< 33 \text{ mV}_{pp}$ |

| Start Input Voltage (rising VIN)       | 7.25 V                 |

| Stop Input Voltage (falling VIN)       | 6.25 V                 |

## Selecting the Switching Frequency

The first step is to decide on a switching frequency for the regulator. Typically, the user will want to choose the highest switching frequency possible since this will produce the smallest solution size. The high switching frequency allows for lower valued inductors and smaller output capacitors compared to a power supply that switches at a lower frequency. The switching frequency that can be selected is limited by the minimum on-time of the internal power switch, the input voltage and the output voltage and the frequency shift limitation.

Equation 12 and Equation 13 must be used to find the maximum switching frequency for the regulator, choose the lower value of the two equations. Switching frequencies higher than these values will result in pulse skipping or the lack of overcurrent protection during a short circuit.

The typical minimum on time,  $t_{onmin}$ , is 130 ns for the TPS54160. For this example, the output voltage is 3.3 V and the maximum input voltage is 18 V, which allows for a maximum switch frequency up to 1600 kHz when including the inductor resistance, on resistance and diode voltage in Equation 12. To ensure overcurrent runaway is not a concern during short circuits in your design use Equation 13 or the solid curve in Figure 42 to determine the maximum switching frequency. With a maximum input voltage of 20 V, for some margin above 18 V, assuming a diode voltage of 0.5 V, inductor resistance of 100 m $\Omega$ , switch resistance of 200m $\Omega$ , a current limit value of 2.7 A, the maximum switching frequency is approximately 2500kHz.

Choosing the lower of the two values and adding some margin a switching frequency of 1200 kHz is used. To determine the timing resistance for a given switching frequency, use Equation 11 or the curve in Figure 40.

The switching frequency is set by resistor R<sub>t</sub> shown in Figure 51.

Figure 51. High Frequency, 3.3V Output Power Supply Design with Adjusted UVLO.

## Output Inductor Selection (L<sub>o</sub>)

To calculate the minimum value of the output inductor, use Equation 28.

K<sub>IND</sub> is a coefficient that represents the amount of inductor ripple current relative to the maximum output current.

The inductor ripple current will be filtered by the output capacitor. Therefore, choosing high inductor ripple currents will impact the selection of the output capacitor since the output capacitor must have a ripple current rating equal to or greater than the inductor ripple current. In general, the inductor ripple value is at the discretion of the designer; however, the following guidelines may be used.

For designs using low ESR output capacitors such as ceramics, a value as high as  $K_{\text{IND}} = 0.3$  may be used. When using higher ESR output capacitors,  $K_{\text{IND}} = 0.2$  yields better results. Since the inductor ripple current is part of the PWM control system, the inductor ripple current should always be greater than 100 mA for dependable operation. In a wide input voltage regulator, it is best to choose an inductor ripple current on the larger side. This allows the inductor to still have a measurable ripple current with the input voltage at its minimum.

For this design example, use  $K_{IND} = 0.2$  and the minimum inductor value is calculated to be  $7.6\mu H$ . For this design, a nearest standard value was chosen:  $10\mu H$ . For the output filter inductor, it is important that the RMS current and saturation current ratings not be exceeded. The RMS and peak inductor current can be found from Equation 30 and Equation 31.

For this design, the RMS inductor current is 1.506 A and the peak inductor current is 1.62 A. The chosen inductor is a MSS6132-103. It has a saturation current rating of 1.64 A and an RMS current rating of 1.9A.

As the equation set demonstrates, lower ripple currents will reduce the output voltage ripple of the regulator but will require a larger value of inductance. Selecting higher ripple currents will increase the output voltage ripple of the regulator but allow for a lower inductance value.

The current flowing through the inductor is the inductor ripple current plus the output current. During power up, faults or transient load conditions, the inductor current can increase above the calculated peak inductor current level calculated above. In transient conditions, the inductor current can increase up to the switch current limit of the device. For this reason, the most conservative approach is to specify an inductor with a saturation current rating equal to or greater than the switch current limit rather than the peak inductor current.

$$L_{O(min)} = \frac{V_{IN(max)} - V_{OUT}}{I_{OUT} \times K_{IND}} \times \frac{V_{OUT}}{V_{IN(max)} \times f_{SW}}$$

(28)

$$I_{RIPPLE} \le I_{OUT} \times K_{IND}$$

(29)

$$I_{L(rms)} = \sqrt{\left(I_{OUT}\right)^2 + \frac{1}{12} \times \left(\frac{V_{OUT} \times \left(V_{IN(max)} - V_{OUT}\right)}{V_{IN(max)} \times L_O \times f_{SW}}\right)^2}$$

(30)

$$I_{L(peak)} = I_{OUT} + \frac{I_{RIPPLE}}{2}$$

(31)

## **Output Capacitor**

There are three primary considerations for selecting the value of the output capacitor. The output capacitor will determine the modulator pole, the output voltage ripple, and how the regulators responds to a large change in load current. The output capacitance needs to be selected based on the more stringent of these three criteria.

The desired response to a large change in the load current is the first criteria. The output capacitor needs to supply the load with current when the regulator can not. This situation would occur if there are desired hold-up times for the regulator where the output capacitor must hold the output voltage above a certain level for a specified amount of time after the input power is removed. The regulator also will temporarily not be able to supply sufficient output current if there is a large, fast increase in the current needs of the load such as transitioning from no load to a full load. The regulator usually needs two or more clock cycles for the control loop

Incorporated Submit Documentation Feedback

to see the change in load current and output voltage and adjust the duty cycle to react to the change. The output capacitor must be sized to supply the extra current to the load until the control loop responds to the load change. The output capacitance must be large enough to supply the difference in current for twoclock cycles while only allowing a tolerable amount of droop in the output voltage. Equation 32 shows the minimum output capacitance necessary to accomplish this.

Where  $\Delta I_{OUT}$  is the change in output current, fsw is the regulators switching frequency and  $\Delta V_{OUT}$  is the allowable change in the output voltage. For this example, the transient load response is specified as a 4% change in  $V_{OUT}$  for a load step from 0 A (no load) to 1.5 A (full load). For this example,  $\Delta I_{OUT} = 1.5 - 0 = 1.5$  A and  $\Delta V_{OUT} = 0.04 \times 3.3 = 0.132 \text{ V}$ . Using these numbers gives a minimum capacitance of 18.9  $\mu F$ . This value does not take the ESR of the output capacitor into account in the output voltage change. For ceramic capacitors, the ESR is usually small enough to ignore in this calculation. Aluminum electrolytic and tantalum capacitors have higher ESR that should be taken into account.

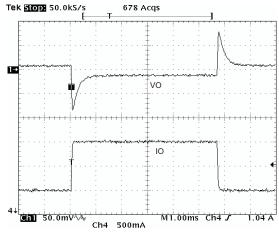

The catch diode of the regulator cannot sink current so any stored energy in the inductor produces an output voltage overshoot when the load current rapidly decreases, see Figure 52. The output capacitor must also be sized to absorb energy stored in the inductor when transitioning from a high load current to a lower load current. The excess energy that gets stored in the output capacitor increases the voltage on the capacitor. The capacitor must be sized to maintain the desired output voltage during these transient periods. Equation 33 is used to calculate the minimum capacitance to keep the output voltage overshoot to a desired value. Where L is the value of the inductor, I<sub>OH</sub> is the output current under heavy load, I<sub>OL</sub> is the output under light load, Vf is the final peak output voltage, and Vi is the initial capacitor voltage. For this example, the worst case load step will be from 1.5 A to 0 A. The output voltage increases during this load transition and the stated maximum in our specification is 4% of the output voltage. This will make  $Vf = 1.04 \times 3.3 = 3.432$ . Vi is the initial capacitor voltage which is the nominal output voltage of 3.3 V. Using these numbers in Equation 33 yields a minimum capacitance of 25.3 μF.

Equation 34 calculates the minimum output capacitance needed to meet the output voltage ripple specification. Where f<sub>SW</sub> is the switching frequency, V<sub>OUT(ripple)</sub> is the maximum allowable output voltage ripple, and I<sub>ripple</sub> is the inductor ripple current. Equation 34 yields 0.7 μf.

Equation 35 calculates the maximum ESR an output capacitor can have to meet the output voltage ripple specification. Equation 35 indicates the ESR should be less than 147 m $\Omega$ .

The most stringent criteria for the output capacitor is 25.3 µF of capacitance to keep the output voltage in regulation during an unload transient.

Additional capacitance de-ratings for aging, temperature and dc bias should be factored in which increases this minimum value. For this example, a 47  $\mu$ F 6.3V X7R ceramic capacitor with 5 m $\Omega$  of ESR is used.

Capacitors generally have limits to the amount of ripple current they can handle without failing or producing excess heat. An output capacitor that can support the inductor ripple current must be specified. Some capacitor data sheets specify the Root Mean Square (RMS) value of the maximum ripple current. Equation 36 can be used to calculate the RMS ripple current the output capacitor needs to support. For this application, Equation 36 yields 64.8 mA.

$$C_{OUT} = \frac{2 \times \Delta I_{OUT}}{f_{SW} \times \Delta V_{OUT}}$$

(32)

$$C_{OUT} > L_{O} \times \frac{\left(\left(l_{OH}\right)^{2} - \left(l_{OL}\right)^{2}\right)}{\left(\left(V_{f}\right)^{2} - \left(V_{i}\right)^{2}\right)}$$

$$C_{OUT} > \frac{1}{8 \times f_{SW}} \times \frac{1}{\left(\frac{V_{OUT(ripple)}}{I_{RIPPLE}}\right)}$$

(33)

$$\frac{C_{\text{OUT}} > \frac{1}{8 \times f_{\text{SW}}} \times \frac{V_{\text{OUT(ripple)}}}{I_{\text{RIPPLE}}}}{(34)}$$

Submit Documentation Feedback

Copyright © 2008-2010, Texas Instruments Incorporated

$$R_{ESR} = \frac{V_{OUT(ripple)}}{I_{RIPPLE}}$$

(35)

$$I_{COUT(rms)} = \frac{V_{OUT} \times \left(V_{IN(max)} - V_{OUT}\right)}{\sqrt{12} \times V_{IN(max)} \times L_O \times f_{SW}}$$

(36)

#### **Catch Diode**

The TPS54160 requires an external catch diode between the PH pin and GND. The selected diode must have a reverse voltage rating equal to or greater than Vinmax. The peak current rating of the diode must be greater than the maximum inductor current. The diode should also have a low forward voltage. Schottky diodes are typically a good choice for the catch diode due to their low forward voltage. The lower the forward voltage of the diode, the higher the efficiency of the regulator.

Typically, the higher the voltage and current ratings the diode has, the higher the forward voltage will be. Since the design example has an input voltage up to 18 V, a diode with a minimum of 20V reverse voltage will be selected.

For the example design, the B220A Schottky diode is selected for its lower forward voltage and it comes in a larger package size which has good thermal characteristics over small devices. The typical forward voltage of the B220A is 0.50 V.

The diode must also be selected with an appropriate power rating. The diode conducts the output current during the off-time of the internal power switch. The off-time of the internal switch is a function of the maximum input voltage, the output voltage, and the switching frequency. The output current during the off-time is multiplied by the forward voltage of the diode which equals the conduction losses of the diode. At higher switch frequencies, the ac losses of the diode need to be taken into account. The ac losses of the diode are due to the charging and discharging of the junction capacitance and reverse recovery. Equation 37 is used to calculate the total power dissipation, conduction losses plus ac losses, of the diode.

The B220A has a junction capacitance of 120pF. Using Equation 37, the selected diode will dissipate 0.632 W. This power dissipation, depending on mounting techniques, should produce a 16°C temperature rise in the diode when the input voltage is 18 V and the load current is 1.5 A.

If the power supply spends a significant amount of time at light load currents or in sleep mode consider using a diode which has a low leakage current and slightly higher forward voltage drop.

$$P_{D} = \frac{\left(V_{IN(max)} - V_{OUT}\right) \times I_{OUT} \times Vfd}{V_{IN(max)}} + \frac{C_{j} \times f_{SW} \times \left(V_{IN} + Vfd\right)^{2}}{2}$$

(37)

#### **Input Capacitor**

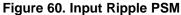

The TPS54160 requires a high quality ceramic, type X5R or X7R, input decoupling capacitor of at least 3  $\mu$ F of effective capacitance and in some applications a bulk capacitance. The effective capacitance includes any dc bias effects. The voltage rating of the input capacitor must be greater than the maximum input voltage. The capacitor must also have a ripple current rating greater than the maximum input current ripple of the TPS54160. The input ripple current can be calculated using Equation 38.

The value of a ceramic capacitor varies significantly over temperature and the amount of dc bias applied to the capacitor. The capacitance variations due to temperature can be minimized by selecting a dielectric material that is stable over temperature. X5R and X7R ceramic dielectrics are usually selected for power regulator capacitors because they have a high capacitance to volume ratio and are fairly stable over temperature. The output capacitor must also be selected with the dc bias taken into account. The capacitance value of a capacitor decreases as the dc bias across a capacitor increases.

For this example design, a ceramic capacitor with at least a 20 V voltage rating is required to support the maximum input voltage. Common standard ceramic capacitor voltage ratings include 4 V, 6.3 V, 10 V, 16 V, 25 V, 50 V or 100 V, so a 25 V capacitor should be selected. For this example, two 2.2  $\mu$ F, 25 V capacitors in parallel have been selected. Table 2 shows a selection of high voltage capacitors. The input capacitance value determines the input ripple voltage of the regulator. The input voltage ripple can be calculated using Equation 39. Using the design example values

- $I_{OUT(max)} = 1.5 A$

- $C_{IN} = 4.4 \mu F$

- $f_{SW} = 1200 \text{ kHz}$

yields an input voltage ripple of 71 mV and a rms input ripple current of 0.701A.